Jörg Henkel Sri Parameswaran *Editors*

# Designing Embedded Processors

A Low Power Perspective

## DESIGNING EMBEDDED PROCESSORS

# **Designing Embedded Processors**

## A Low Power Perspective

Edited by

J.HENKEL University of Karlsruhe, Germany

and

## S.PARAMESWARAN

University of South Wales, NSW, Australia

A C.I.P. Catalogue record for this book is available from the Library of Congress.

ISBN 978-1-4020-5868-4 (HB) ISBN 978-1-4020-5869-1 (e-book)

Published by Springer, P.O. Box 17, 3300 AA Dordrecht, The Netherlands.

www.springer.com

Printed on acid-free paper

All Rights Reserved © 2007 Springer No part of this work may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electronic, mechanical, photocopying, microfilming, recording or otherwise, without written permission from the Publisher, with the exception of any material supplied specifically for the purpose of being entered and executed on a computer system, for exclusive use by the purchaser of the work.

## Contents

| Forew  | ord: Embedded Processors – what is next?                      | XV  |

|--------|---------------------------------------------------------------|-----|

| Jörg H | Ienkel and Sri Parameswaran                                   |     |

| 1.     | Philosophy of This Book                                       | xvi |

| 2.     | Contents                                                      | xvi |

|        |                                                               |     |

| Part I | Application Specific Embedded Processors                      |     |

| 1      |                                                               |     |

| Applic | cation-Specific Embedded Processors                           | 3   |

| Jörg H | Ienkel, Sri Parameswaran, and Newton Cheung                   |     |

| 1.     | Introduction and Motivation                                   | 4   |

|        | 1.1 Some Trends in Designing SOCs                             | 6   |

|        | 1.2 Extensible Processor Platforms as a Possible Solution     | 7   |

|        | 1.3 Open Issues and Key Techniques                            | 10  |

|        | 1.4 SOC Design Distinction                                    | 11  |

| 2.     | Challenges in Embedded Extensible Processor Design            | 12  |

|        | 2.1 Code Segment Identification                               | 12  |

|        | 2.2 Extensible Instruction Generation                         | 14  |

|        | 2.3 Architectural Customization Selection                     | 17  |

|        | 2.4 Summary                                                   | 19  |

| Re     | ferences                                                      | 19  |

| 2      |                                                               |     |

| Low-F  | Power Design with NISC Technology                             | 25  |

| Bita G | orjiara, Mehrdad Reshadi, and Daniel Gajski                   |     |

| 1.     | Introduction                                                  | 25  |

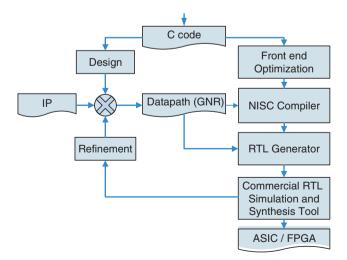

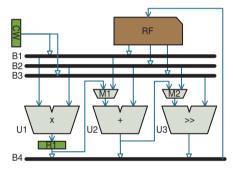

| 2.     | Overview of NISC Technology                                   | 27  |

| 3.     | NISC Compared to Other Approaches                             | 29  |

|        | 3.1 NISC vs. ASIP                                             | 29  |

|        | 3.2 NISC vs. VLIW                                             | 30  |

|        | 3.3 NISC vs. Microcoded Architectures                         | 30  |

|        | 3.4 NISC vs. HLS                                              | 31  |

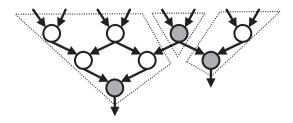

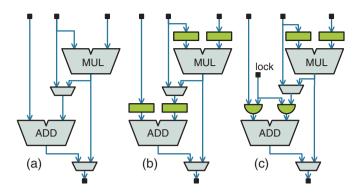

|        | Overview of the Compilation Algorithm                         | 32  |

| 5.     | Power Optimizations in NISC                                   | 37  |

|        | 5.1 Reducing the Switching Capacitance                        | 37  |

|        | 5.2 Reducing Number of Cycles                                 | 39  |

| 6.     | Experiments                                                   | 39  |

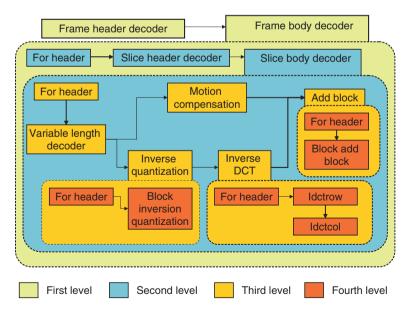

|        | 6.1 The Effect of Pipeline Structure on Power and Performance | 39  |

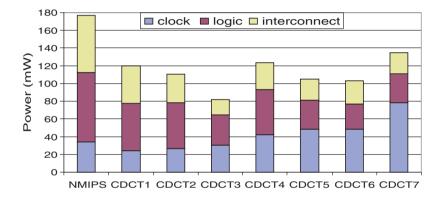

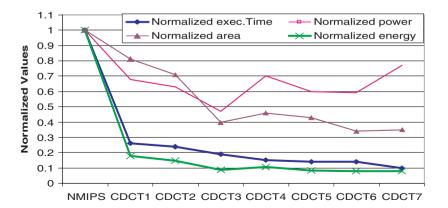

|        | 6.2 Custom Datapath Design for DCT                            | 42  |

| 7. Conclusion<br>References                                                                | 49<br>49 |

|--------------------------------------------------------------------------------------------|----------|

| 3                                                                                          |          |

| Synthesis of Instruction Sets for High-Performance and Energy-Efficient ASIP               | nt 51    |

| Jong-Eun Lee, Kiyoung Choi, and Nikil D. Dutt                                              |          |

| 1. Introduction                                                                            | 52       |

| 2. Related Work                                                                            | 53       |

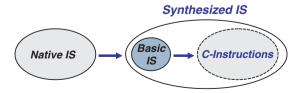

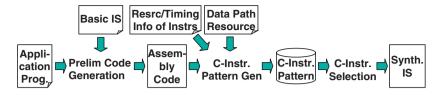

| 3. Synthesizing Instruction Sets                                                           | 54       |

| 4. Optimizing for Energy-Efficiency                                                        | 55       |

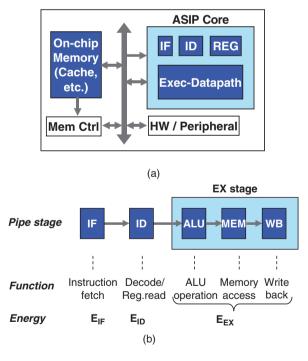

| 4.1 ASIP Energy Model                                                                      | 56       |

| 4.2 EDP Change due to IS Customization                                                     | 57       |

| 4.3 Modifying the Selection Algorithm                                                      | 58       |

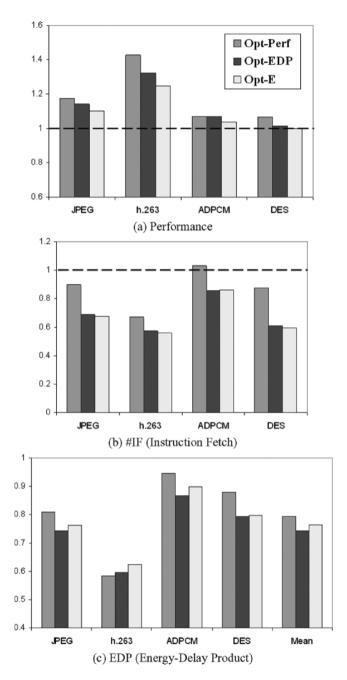

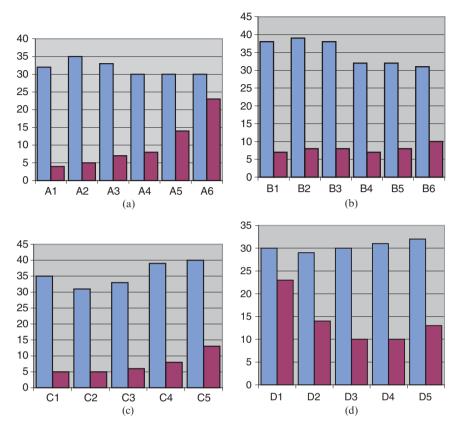

| 5. Experiments                                                                             | 58       |

| 5.1 Experimental Setup                                                                     | 59       |

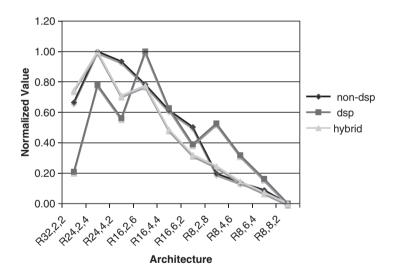

| 5.2 Improvement through IS Synthesis                                                       | 60       |

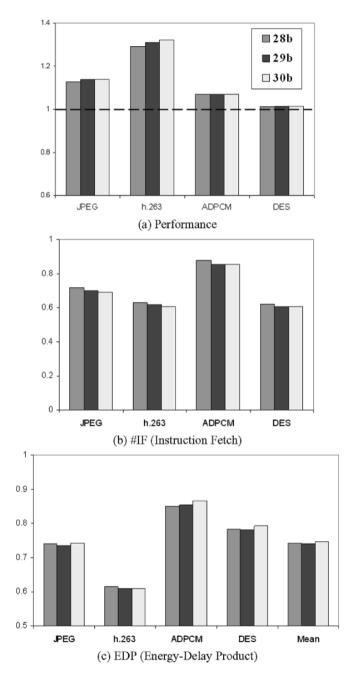

| 5.3 Effects of Bitwidth Variation                                                          | 63       |

| 6. Conclusion                                                                              | 63       |

| References                                                                                 | 64       |

|                                                                                            | 65       |

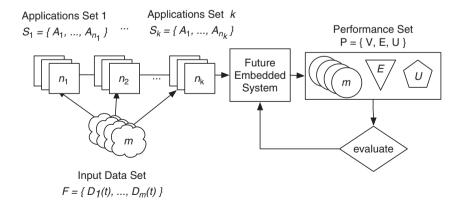

| A Framework for Extensible Processor Based MPSoC Design                                    | 03       |

| Fei Sun, Srivaths Ravi, Anand Raghunathan, and Niraj K. Jha                                |          |

| 1. Introduction                                                                            | 66       |

| 2. Overview of MPSoC Synthesis                                                             | 67       |

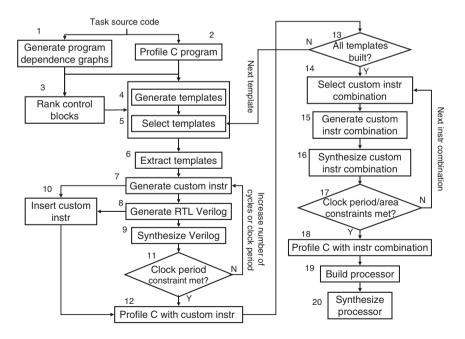

| 3. Custom Processor Synthesis                                                              | 69       |

| 3.1 Motivation                                                                             | 70       |

| 3.2 Extensible Processor Synthesis Methodology                                             | 71       |

| 3.3 Template Generation                                                                    | 72       |

| 3.4 Experimental Results                                                                   | 75       |

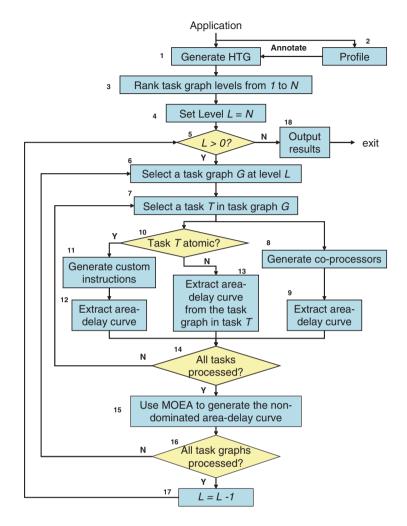

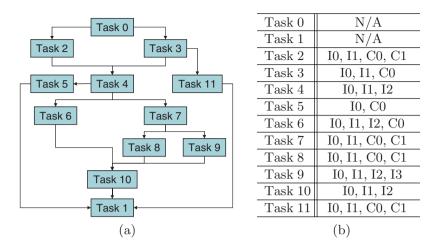

| 4. Hybrid Custom Instruction and Co-Processor Synthesis                                    | 77       |

| 4.1 Methodology Overview                                                                   | 77       |

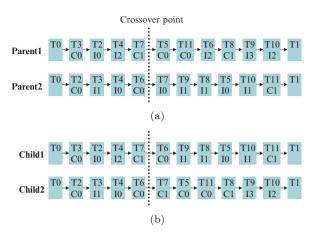

| 4.2 Multiobjective Evolutionary Algorithm                                                  | 79       |

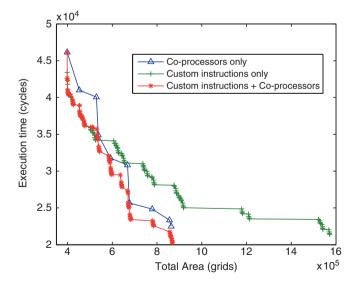

| 4.3 Experimental Results                                                                   | 81       |

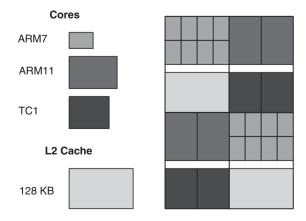

| 5. Heterogeneous Multiprocessor Synthesis                                                  | 84       |

| 5.1 Basic Synthesis Methodology                                                            | 84       |

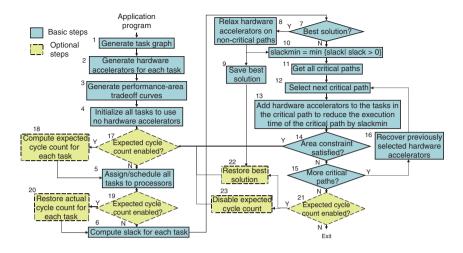

| 5.2 Enhanced Synthesis Methodology                                                         | 87       |

| 5.3 Experimental Results                                                                   | 88       |

| 6. Related Work                                                                            | 92       |

| 7. Conclusions                                                                             | 93       |

| References                                                                                 | 93       |

|                                                                                            | 07       |

| Design and Run Time Code Compression for Embedded Systems                                  | 97       |

| Sri Parameswaran, Jörg Henkel, Andhi Janapsatya, Talal Bonny,<br>and Aleksandar Ignjatovic |          |

| 1. Introduction                                                                            | 98       |

| 1.1 Design Time Compression                                                                | 98       |

| 1.2 Run Time Code Compression                                                              | 100      |

| 2. | Rela  | ited Work                                                    | 100 |

|----|-------|--------------------------------------------------------------|-----|

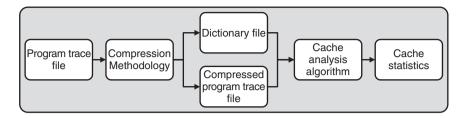

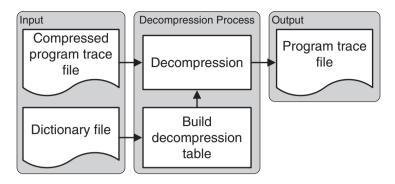

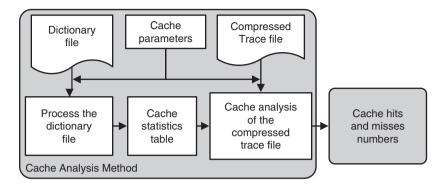

| 3. | Des   | ign Time – Cache Trace Compression and Cache Size Prediction | 103 |

|    | 3.1   | Methodology                                                  | 103 |

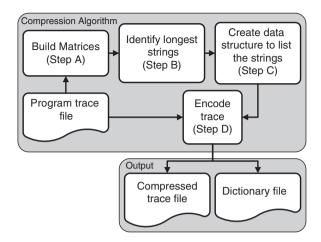

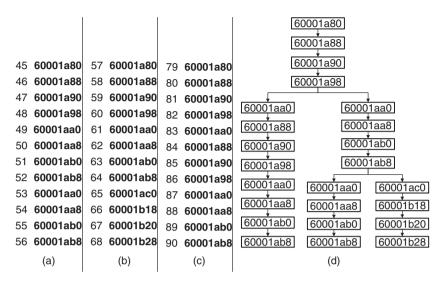

|    | 3.2   | Compression Algorithm                                        | 103 |

|    | 3.3   | Cache Simulation Algorithm                                   | 109 |

|    | 3.4   | Experimental Setup and Results                               | 111 |

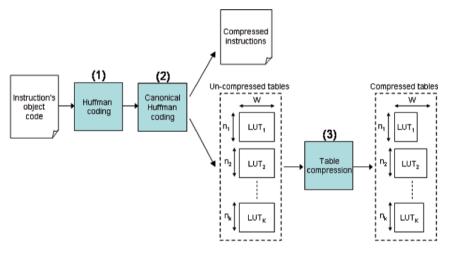

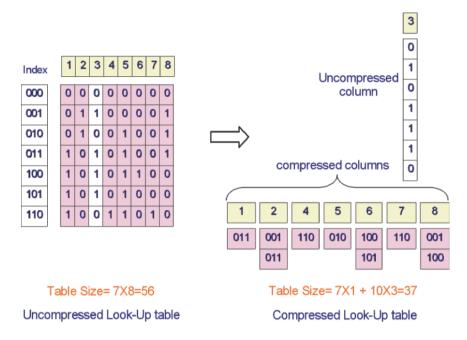

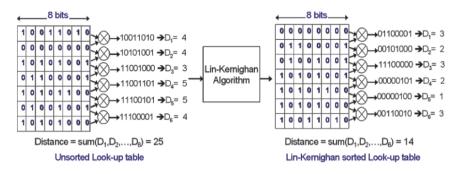

| 4. | Run   | Time – Code Compression                                      | 114 |

|    | 4.1   | Code Compression Technique                                   | 114 |

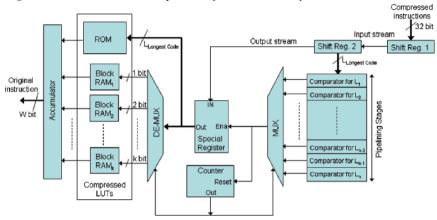

|    |       | Hardware Implementation                                      | 119 |

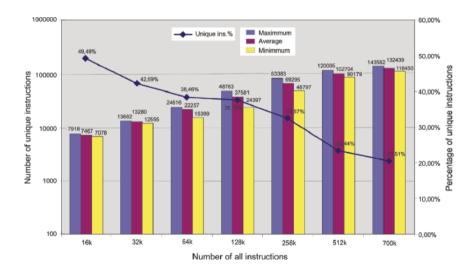

|    | 4.3   | Experiments and Results                                      | 121 |

|    | 4.4   | Conclusion                                                   | 124 |

| Re | feren | ces                                                          | 125 |

#### Part II Embedded Memories

| 6                                                                   |     |

|---------------------------------------------------------------------|-----|

| Power Optimisation Strategies Targeting the Memory Subsystem        | 131 |

| Preeti Ranjan Panda                                                 |     |

| 1. Introduction                                                     | 131 |

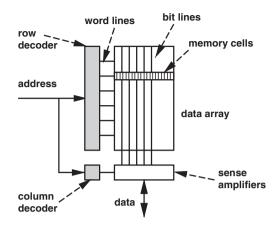

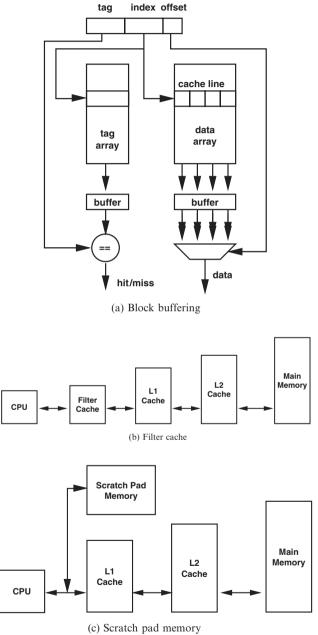

| 2. Power-Efficient Memory Architectures                             | 133 |

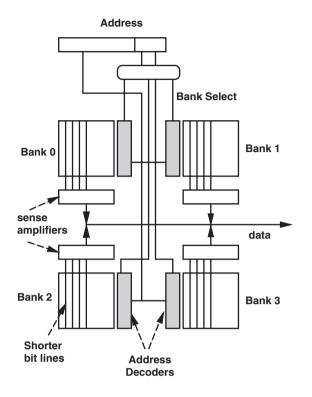

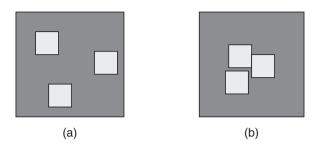

| 2.1 Partitioned Memory and Caches                                   | 133 |

| 2.2 Augmenting with Additional Buffers/Caches                       | 134 |

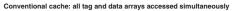

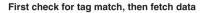

| 2.3 Reducing Tag Comparison Power                                   | 137 |

| 2.4 Reducing Cache Leakage Power                                    | 139 |

| 2.5 Other Cache Ideas                                               | 140 |

| 3. Compiler Optimisations Targeting Memory Power                    | 141 |

| 3.1 Data Layout                                                     | 142 |

| 3.2 Instruction Layout                                              | 142 |

| 3.3 Scratch Pad Memory Utilisation                                  | 143 |

| 3.4 Memory Bank Utilisation                                         | 144 |

| 4. Application Specific Memory Customisation                        | 145 |

| 5. Other Techniques: Dynamic Voltage Scaling,                       |     |

| Compression, Encoding, etc.                                         | 146 |

| 5.1 Dynamic Voltage Scaling                                         | 147 |

| 5.2 Power Management in DRAM                                        | 147 |

| 5.3 Encoding                                                        | 148 |

| 5.4 Compression                                                     | 148 |

| References                                                          | 150 |

| 7                                                                   |     |

| Layer Assignment Techniques for Low Energy in Multi-Layered Memory  | 157 |

| Organizations                                                       |     |

| Erik Brockmeyer, Bart Durinck, Henk Corporaal, and Francky Catthoor |     |

| 1. Introduction                                                     | 158 |

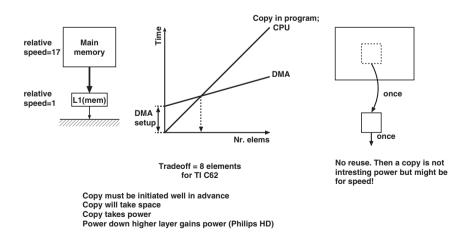

| 2. Basic Problem Definition                                         | 160 |

| 2.1 Data Reuse Analysis                                             | 161 |

| 2.2 Memory Hierarchy Assignment                                     | 162 |

| 2.3 Power, Area and Time Trade-off                                  | 165 |

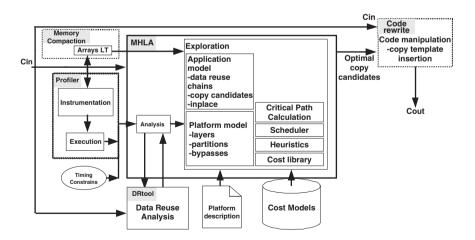

| 2.4 Overall Methodology for MHLA                                    | 166 |

| Contents |

|----------|

|----------|

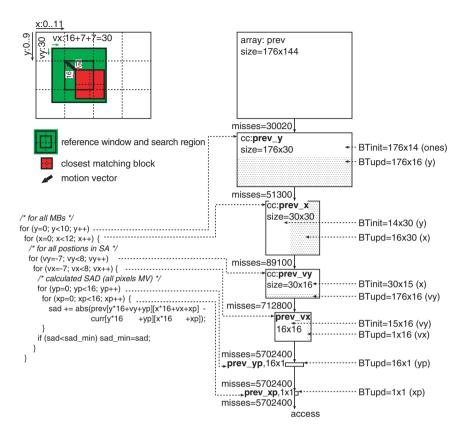

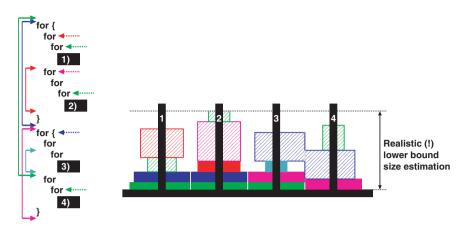

| 3. Data Reuse Analysis                                            | 167 |

|-------------------------------------------------------------------|-----|

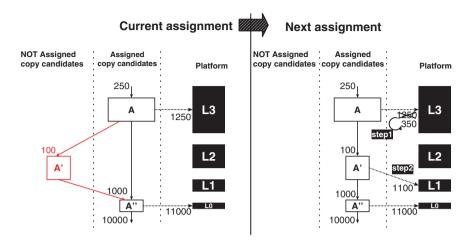

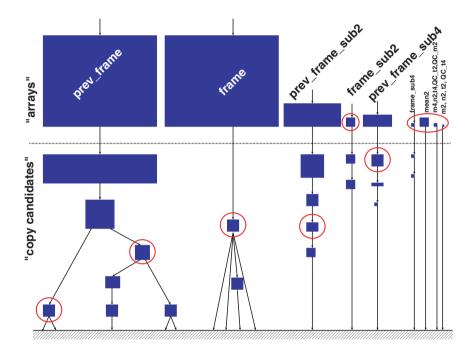

| 3.1 Copy Candidates                                               | 168 |

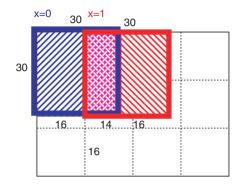

| 3.2 Block Transfers                                               | 168 |

| 3.3 Non-Carried Copy Candidates                                   | 170 |

| 3.4 Branches in Reuse Tree                                        | 172 |

| 3.5 Write Accesses in the Reuse Tree                              | 173 |

| 4. High-Level Estimations                                         | 173 |

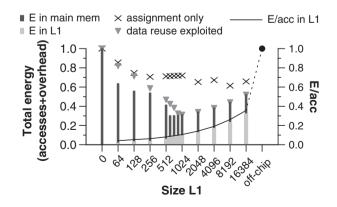

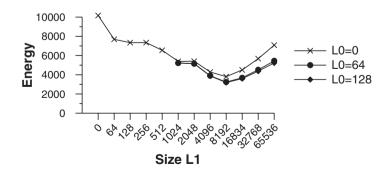

| 4.1 Energy Estimation                                             | 173 |

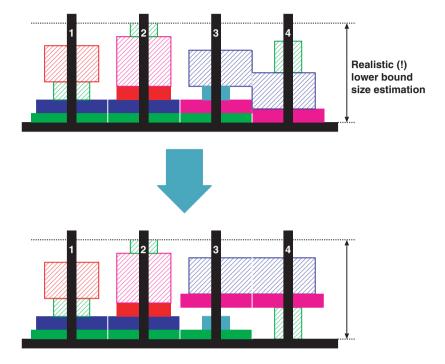

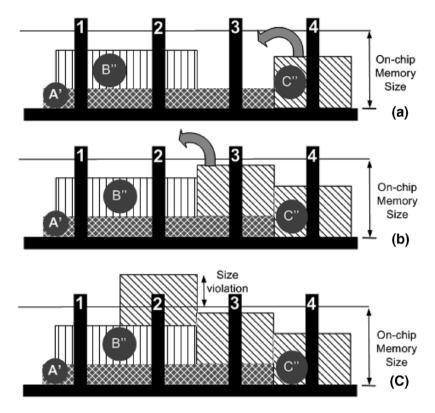

| 4.2 Size Estimation                                               | 173 |

| 4.3 Time Estimation                                               | 175 |

| 5. Exploration Methodology for MHLA Search Space                  | 182 |

| 5.1 Steering Heuristic                                            | 182 |

| 5.2 Incremental Assignment                                        | 182 |

| 6. Case Studies                                                   | 183 |

| 6.1 QSDPCM                                                        | 183 |

| 6.2 DAB Wireless Receiver                                         | 185 |

| 6.3 Execution Time Measurements                                   | 186 |

| 7. Related Work                                                   | 186 |

| 8. Conclusion and Future Work                                     | 188 |

| References                                                        | 188 |

| 8                                                                 |     |

| Memory Bank Locality and Its Usage in Reducing Energy Consumption | 191 |

| Mahmut Kandemir                                                   |     |

| 1. Introduction and Motivation                                    | 191 |

| 2. Banked Memory Architecture and Low-Power Operating Modes       | 193 |

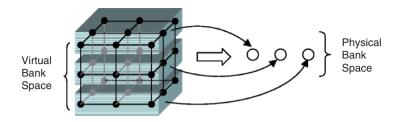

| 3. Affine Mappings of Arrays to Banks                             | 195 |

| 4. Constraints for Bank Locality                                  | 197 |

| 5. Loop Transformations for Bank Locality                         | 198 |

| 6. Implementing Array Decompositions                              | 202 |

| 7. Global Optimizations                                           | 203 |

| 7.1 Single Nest, Multiple Arrays                                  | 203 |

| 7.2 Multiple Nest, Single Array                                   | 204 |

| 7.3 Multiple Nests, Multiple Arrays                               | 206 |

| 7.4 Discussion                                                    | 207 |

| 8. Folding Functions                                              | 207 |

| 9. Experiments                                                    | 208 |

| 9.1 Benchmark Codes and Experimental Framework                    | 208 |

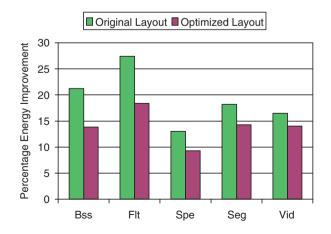

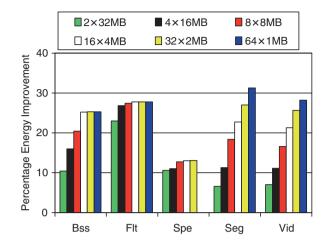

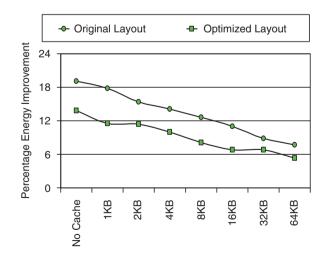

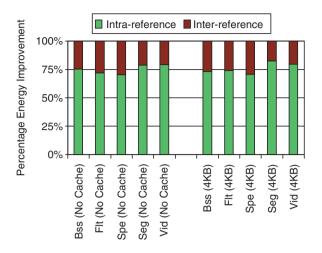

| 9.2 Results                                                       | 210 |

| 10. Concluding Remarks and Future Work                            | 210 |

| References                                                        | 214 |

| Kelelences                                                        | 215 |

| Part III Dynamic Voltage and Frequency Scaling                    |     |

| 9                                                                 |     |

| Fundamentals of Power-Aware Scheduling                            | 219 |

| Xiaobo Sharon Hu and Gang Quan                                    |     |

| Contents                                                                             | ix  |

|--------------------------------------------------------------------------------------|-----|

| 3. Basics in Real-Time Scheduling                                                    | 222 |

| 4. Impacts of Power-Aware Scheduling                                                 | 223 |

| 5. Further Reading                                                                   | 224 |

| 5.1 Application Characteristics                                                      | 224 |

| 5.2 Scheduling Decisions                                                             | 225 |

| 5.3 Architectures                                                                    | 226 |

| References                                                                           | 226 |

| 10                                                                                   | 221 |

| Static DVFS Scheduling                                                               | 231 |

| Gang Quan and Xiaobo Sharon Hu                                                       | 021 |

| 1. Introduction                                                                      | 231 |

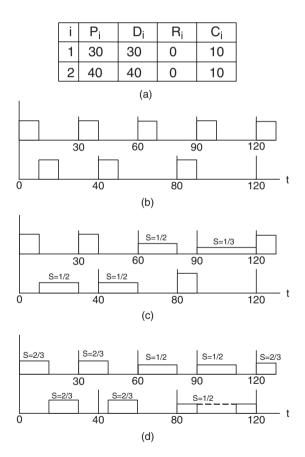

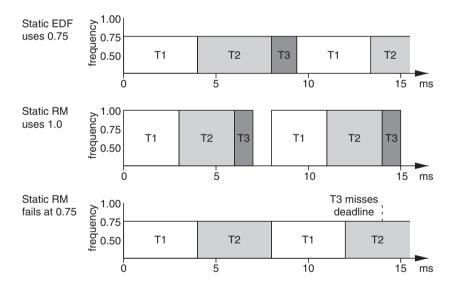

| 2. EDF Scheduling                                                                    | 232 |

| 3. Fixed-Priority Scheduling                                                         | 233 |

| 3.1 Determining the Minimum Constant Speed for Each Job                              | 235 |

| 3.2 Determining the Global Voltage Schedule                                          | 239 |

| 4. Related Work                                                                      | 240 |

| References                                                                           | 241 |

| 11<br>Description DVEC Caladation                                                    | 243 |

| Dynamic DVFS Scheduling                                                              | 243 |

| Padmanabhan S. Pillai and Kang G. Shin                                               | 242 |

| 1. Introduction                                                                      | 243 |

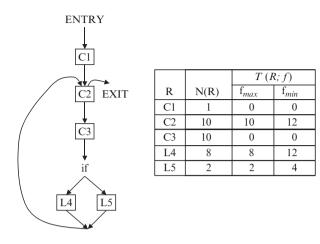

| 2. Schedulability Constraints for EDF and RM                                         | 244 |

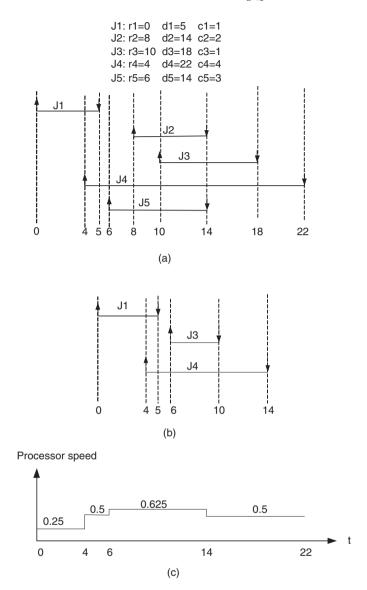

| 3. Cycle-Conserving, Real-time DVFS                                                  | 245 |

| 3.1 Cycle-Conserving EDF                                                             | 247 |

| 3.2 Cycle-Conserving RM                                                              | 249 |

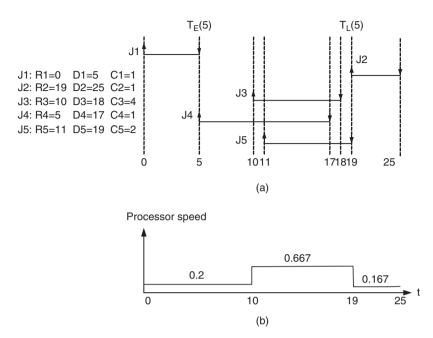

| 4. Look-ahead DVFS                                                                   | 252 |

| 5. Evaluating Energy Performance of DVFS Algorithms                                  | 255 |

| 6. Related Readings                                                                  | 257 |

| References                                                                           | 257 |

| 12<br>Voltage Selection for Time-Constrained                                         | 259 |

| Multiprocessor Systems                                                               | 207 |

| Alexandru Andrei, Petru Eles, Zebo Peng, Marcus Schmitz,<br>and Bashir M. Al-Hashimi |     |

| 1. Introduction                                                                      | 260 |

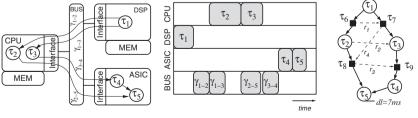

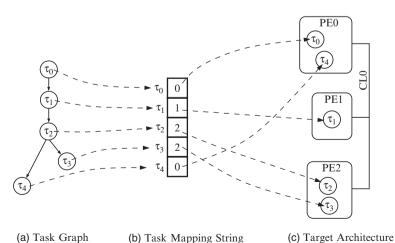

| 2. System and Application Model                                                      | 261 |

| 3. Processor Power and Delay Models                                                  | 262 |

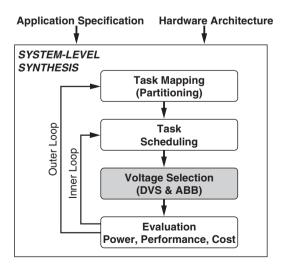

| 4. Optimization of Mapping and Schedule for Voltage Selection                        | 262 |

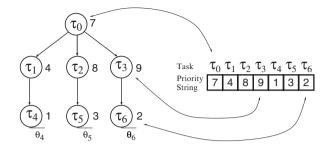

| 4.1 Genetic Task Mapping Algorithm                                                   | 265 |

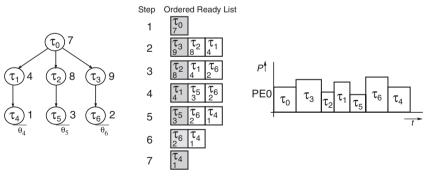

| 4.2 Genetic Scheduling Algorithm                                                     | 265 |

| 5. Motivational Example                                                              | 269 |

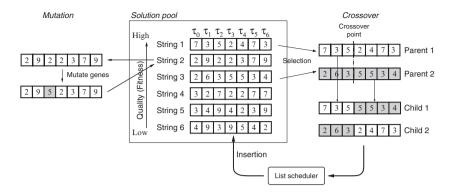

| 5.1 Optimizing the Dynamic and Leakage Energy                                        | 269 |

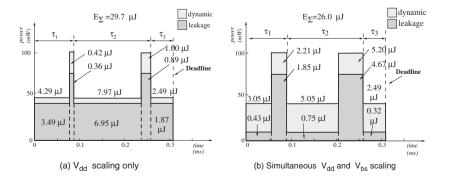

| 5.2 Considering the Transition Overheads                                             | 20) |

| 6. Problem Formulation                                                               | 270 |

|                                                                                      | 212 |

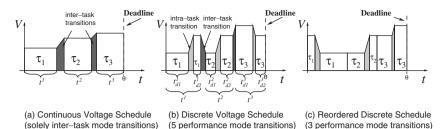

| 7. Optimal Continuous Voltage Selection               | 272                 |

|-------------------------------------------------------|---------------------|

| 7.1 Continuous Voltage Selection without Ov           | verheads (CNOH) 272 |

| 7.2 Continuous Voltage Selection with Overl           | neads (COH) 274     |

| 8. Optimal Discrete Voltage Selection                 | 274                 |

| 8.1 Problem Complexity                                | 274                 |

| 8.2 Discrete Voltage Selection without Overl          |                     |

| 8.3 Discrete Voltage Selection with Overhead          | ds (DOH) 276        |

| 8.4 Discrete Voltage Selection Heuristic              | 278                 |

| 9. Experimental Results                               | 279                 |

| 10. Related Work                                      | 280                 |

| 11. Summary                                           | 281                 |

| References                                            | 282                 |

| Part IV Compiler Techniques                           |                     |

| 13                                                    |                     |

| Compilation Techniques for Power, Energy,             | 287                 |

| and Thermal Management                                |                     |

| Ulrich Kremer                                         |                     |

| 1. Optimizing Compilers                               | 287                 |

| 2. Optimization Metrics                               | 289                 |

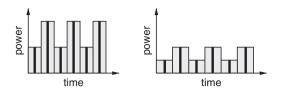

| 2.1 Power vs. Energy                                  | 289                 |

| 2.2 Power/Energy vs. Performance                      | 292                 |

| 2.3 Power/Energy vs. Temperature                      | 295                 |

| 2.4 Summary                                           | 296                 |

| 3. Future Compiler Research Directions                | 297                 |

| 4. Techniques Covered in Subsequent Chapters          | 298                 |

| 4.1 Dynamic Voltage and Frequency Scaling             |                     |

| 4.2 Resource Hibernation                              | 299                 |

| 4.3 Remote Task Mapping                               | 299                 |

| References                                            | 300                 |

| 14<br>Compiler-Directed Dynamic CPU Frequency and Vol | tage Scaling 305    |

| Chung-Hsing Hsu and Ulrich Kremer                     |                     |

| 1. DVFS                                               | 305                 |

| <ol> <li>DVFS Scheduling is Challenging</li> </ol>    | 306                 |

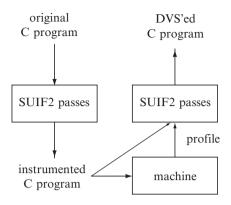

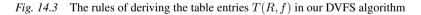

| 3. Our DVFS Algorithm in a Nutshell                   | 307                 |

| 4. An Illustrating Example                            | 308                 |

| 5. Design and Implementation Issues                   | 311                 |

| 5.1 What is a Region                                  | 311                 |

| 5.2 How Many Regions to Slow Down                     | 312                 |

| 5.3 What Region to Pick                               | 312                 |

| 5.4 Why Compiler-Directed                             | 313                 |

| 5.5 Is Profile-Driven Necessary                       | 313                 |

| 6. Evaluation Strategy                                | 314                 |

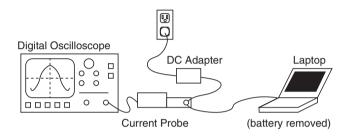

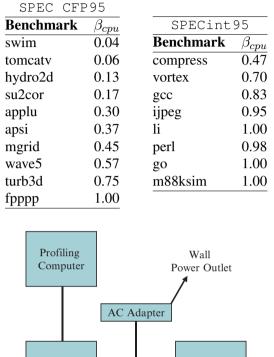

| 6.1 Hardware Platform                                 | 314                 |

| 6.2 Software Platform                                 | 314                 |

| 6.3 Benchmark Choices                                 | 315                 |

| Contents                                                                                                                                                                                | xi                              |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|

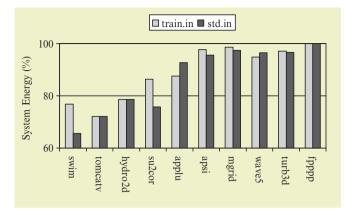

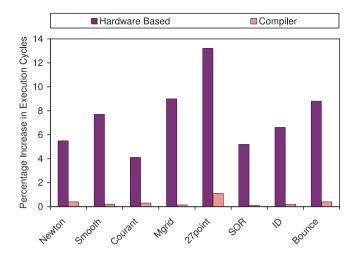

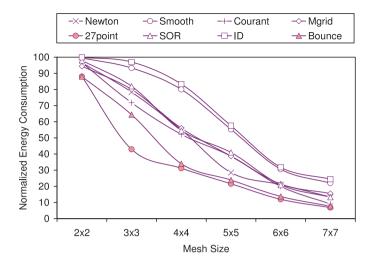

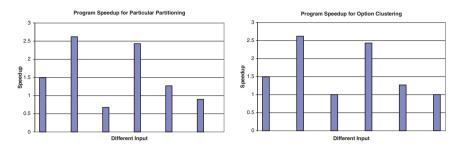

| <ol> <li>7. Experimental Results</li> <li>7.1 The Compilation Time</li> <li>7.2 Effectiveness</li> <li>7.3 Different Training Inputs</li> <li>8. Conclusions and Future Work</li> </ol> | 317<br>317<br>318<br>319<br>321 |

| References                                                                                                                                                                              | 322                             |

|                                                                                                                                                                                         | 324                             |

| 15<br>Link Idle Period Exploitation for Network Power Management                                                                                                                        | 325                             |

| Feihui Li, Guangyu Chen, Mahmut Kandemir, and Mustafa Karakoy                                                                                                                           | 525                             |

| 1. Introduction                                                                                                                                                                         | 326                             |

| 2. Experimental Setup                                                                                                                                                                   | 327                             |

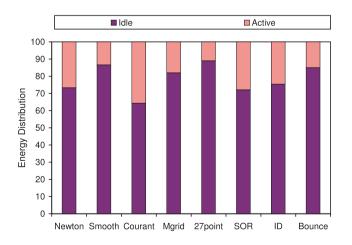

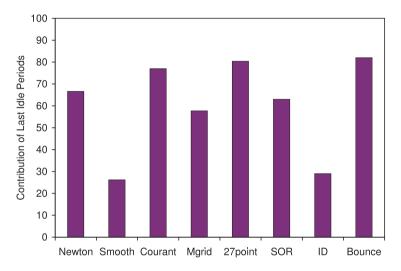

| 3. Quantification of Last Idle Times                                                                                                                                                    | 329                             |

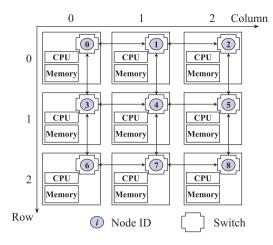

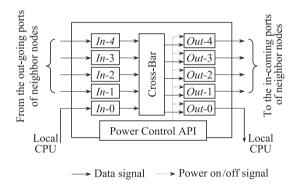

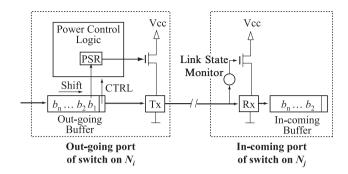

| 4. Network Abstraction and Hardware Support                                                                                                                                             | 330                             |

| 5. Compiler Support                                                                                                                                                                     | 333                             |

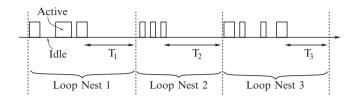

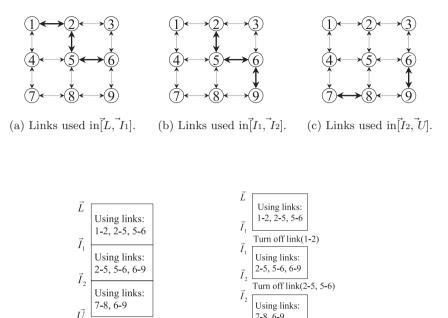

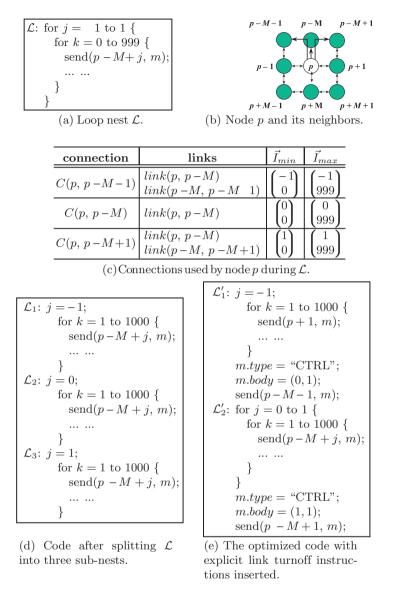

| 5.1 Splitting Loop Nests                                                                                                                                                                | 334                             |

| 5.2 Inserting Link Turn-off Instructions                                                                                                                                                | 337                             |

| 5.3 Example                                                                                                                                                                             | 338                             |

| 5.4 Discussion                                                                                                                                                                          | 340                             |

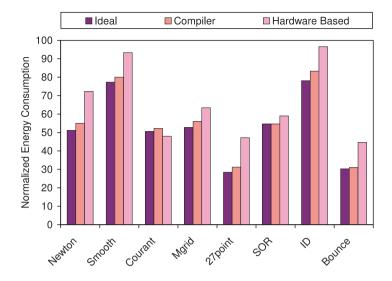

| 6. Experimental Results                                                                                                                                                                 | 340                             |

| 7. Concluding Remarks                                                                                                                                                                   | 343                             |

| References                                                                                                                                                                              | 344                             |

| 16                                                                                                                                                                                      |                                 |

| Remote Task Mapping                                                                                                                                                                     | 347                             |

| Zhiyuan Li and Cheng Wang                                                                                                                                                               |                                 |

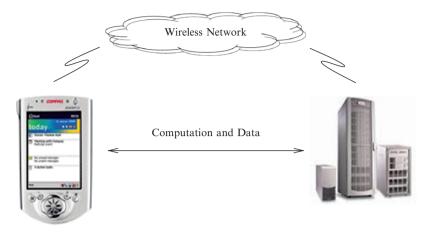

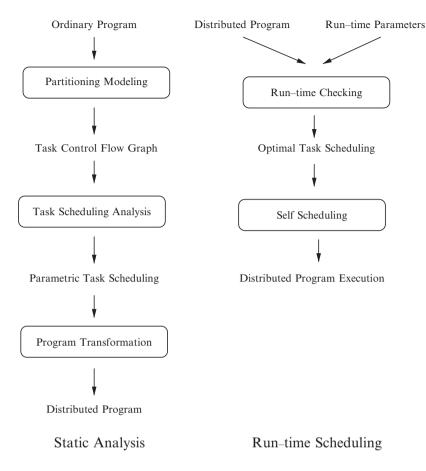

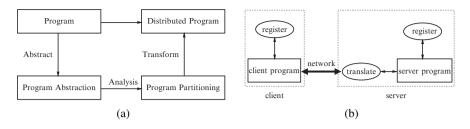

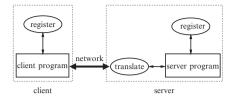

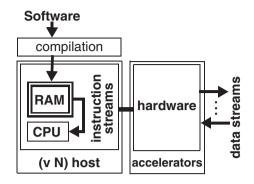

| 1. Computation Offloading on Handheld Devices                                                                                                                                           | 347                             |

| 1.1 An Overview                                                                                                                                                                         | 349                             |

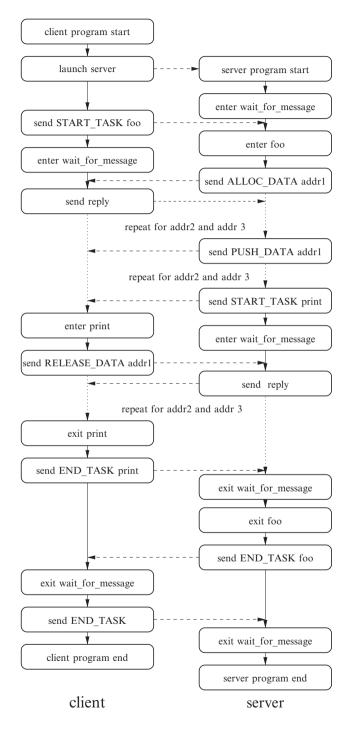

| 1.2 The Execution Model                                                                                                                                                                 | 351                             |

| 1.3 Message Passing                                                                                                                                                                     | 352                             |

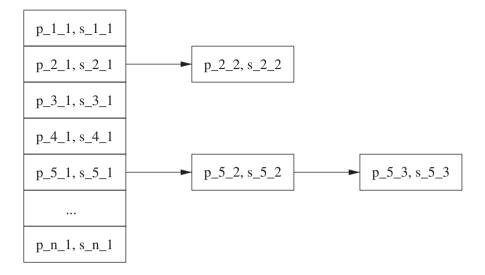

| <ul><li>1.4 A Number of Primitives</li><li>1.5 Code Generation</li></ul>                                                                                                                | 353<br>357                      |

| 1.6 Task-Assignment Analysis                                                                                                                                                            | 360                             |

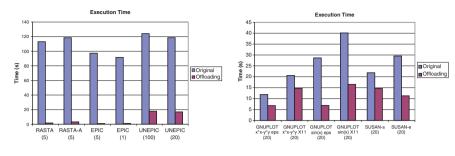

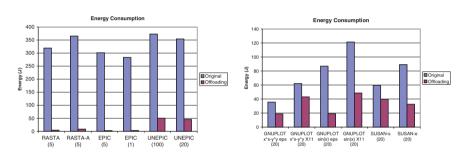

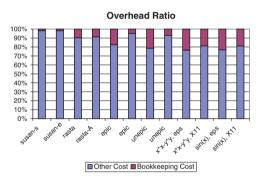

| 1.7 Experiments                                                                                                                                                                         | 365                             |

| 1.8 Related Work                                                                                                                                                                        | 369                             |

| References                                                                                                                                                                              | 369                             |

| Part V Multi-Processors                                                                                                                                                                 |                                 |

|                                                                                                                                                                                         |                                 |

| 17                                                                                                                                                                                      | 272                             |

| A Power and Energy Perspective on MultiProcessors                                                                                                                                       | 373                             |

| Grant Martin 1. Introduction                                                                                                                                                            | 373                             |

| 1.1 Multicore and Multiprocessor Definitions                                                                                                                                            | 373                             |

| 1.2 Power/Energy Drivers for Multiprocessor                                                                                                                                             | 574                             |

| and Multicore Architectures                                                                                                                                                             | 376                             |

| 1.3 Classifying Multiprocessor Architectures                                                                                                                                            | 378                             |

|                                                                                                                                                                                         |                                 |

| 2.    | A Survey of Multiprocessor Approaches                             |     |

|-------|-------------------------------------------------------------------|-----|

|       | for Low-Power, Low-Energy Design                                  | 379 |

|       | 2.1 Basic Techniques                                              | 379 |

|       | 2.2 Formal Control of DVFS for CMP                                | 382 |

|       | 2.3 Use of Transactional Memory in Multiprocessor Systems         | 383 |

| 3.    | Asymmetric Multiprocessing                                        | 383 |

|       | 3.1 Multiprocessor Systems of Configurable, Extensible Processors | 383 |

| 4.    | Techniques Covered in Subsequent Chapters                         | 385 |

|       | 4.1 Power-Performance Modeling and Design                         |     |

|       | for Heterogeneous Multiprocessors                                 | 385 |

|       | 4.2 System-Level Design of Network-on-Chip Architectures          | 386 |

|       | Conclusion                                                        | 387 |

| R     | eferences                                                         | 388 |

| 18    |                                                                   |     |

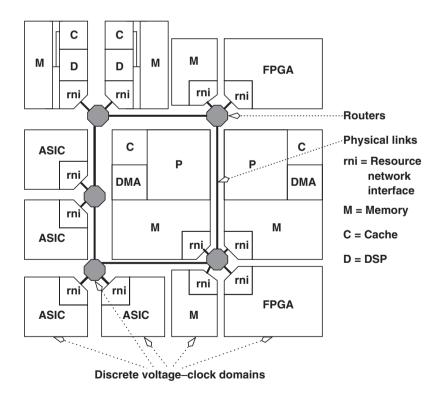

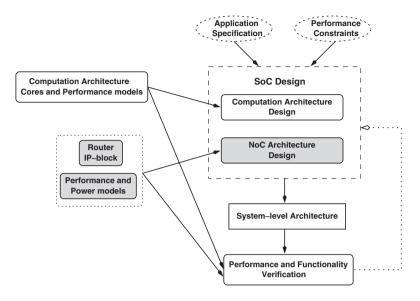

| Syste | m-Level Design of Network-on-Chip Architectures                   | 391 |

| Kara  | m S. Chatha and Krishnan Srinivasan                               |     |

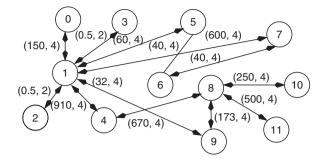

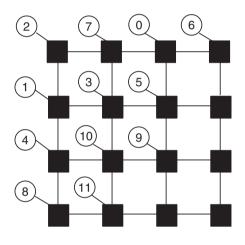

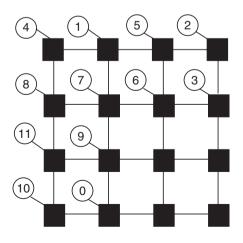

| 1.    | Introduction                                                      | 392 |

|       | 1.1 Multi-Processor System-on-Chip (MPSoC) Architectures          | 392 |

|       | 1.2 Interconnection Woes and Network-on-Chip (NoC)                | 392 |

|       | 1.3 IP-based Methodology for NoC Design                           | 394 |

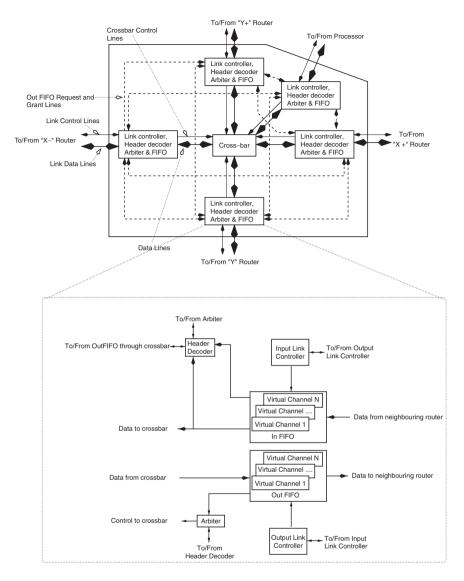

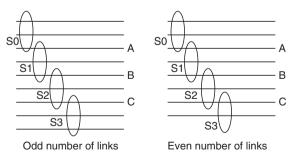

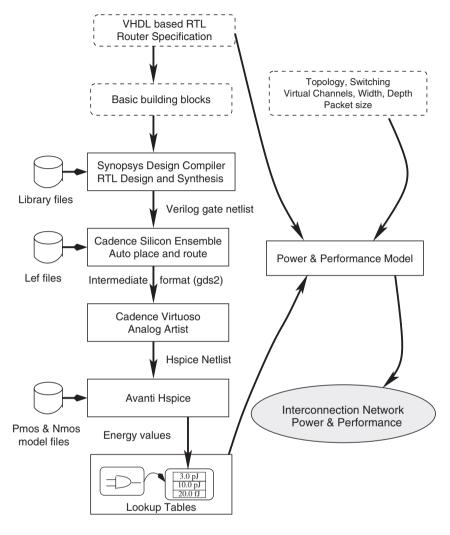

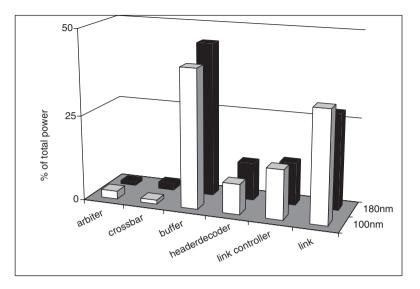

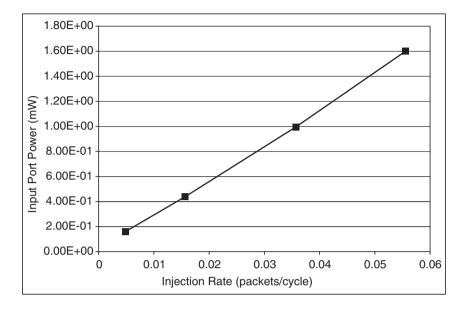

| 2.    | NoC Router Architecture and Characterization                      | 395 |

|       | 2.1 NoC Router Architecture                                       | 396 |

|       | 2.2 Power and Performance Characterization                        | 398 |

|       | 2.3 Elements of NoC Design Process                                | 399 |

| 3.    | Design and Optimization Techniques for NoC                        | 404 |

|       | 3.1 MILP based Approach                                           | 405 |

|       | 3.2 Heuristic Approach                                            | 410 |

|       | 3.3 MOCA Phase I: Core to Router Mapping                          | 410 |

|       | 3.4 MOCA Phase II: Route Generation                               | 411 |

| 4.    | Related Research                                                  | 415 |

|       | 4.1 NoC Router Architectures                                      | 415 |

|       | 4.2 NoC Performance and Power Consumption Models                  | 416 |

|       | 4.3 NoC Design and Optimization Techniques                        | 416 |

|       | Conclusion                                                        | 416 |

| R     | eferences                                                         | 417 |

| 19    |                                                                   |     |

|       | r-Performance Modeling and Design                                 | 423 |

|       | or Heterogeneous Multiprocessors                                  |     |

| JoAn  | n M. Paul and Brett H. Meyer                                      |     |

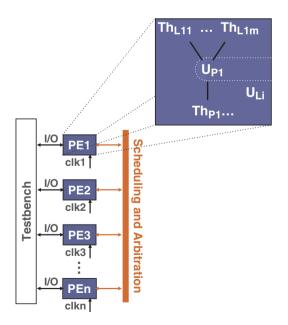

| 1.    |                                                                   | 423 |

| 2.    |                                                                   | 424 |

| 3.    | MESH                                                              | 425 |

|       | 3.1 MESH as a Performance Simulator                               | 426 |

|       | 3.2 Energy Modeling in MESH                                       | 428 |

|       | 3.3 Power-Performance Design Evaluation in MESH                   | 429 |

| 4.    | Performance Evaluation of SCHMs                                   | 430 |

|       | 4.1 Application Performance Classification                        | 432 |

| Contents                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | xiii                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| <ul> <li>4.2 Arrival Characteristics and Timing</li> <li>4.3 Observations</li> <li>5. Heterogeneous Performance Balance</li> <li>5.1 Processing Elements</li> <li>5.2 Applications and System Scheduling</li> <li>5.3 Tiles and the Tiled System</li> <li>5.4 Modeling Assumptions</li> <li>5.5 Experiments and Results</li> <li>5.6 Discussion</li> <li>6. Conclusions</li> <li>References</li> </ul>                                                                                                                                      | 432<br>434<br>435<br>435<br>438<br>439<br>440<br>441<br>445<br>445<br>446 |

| Part VI Reconfigurable Computing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                           |

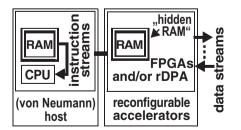

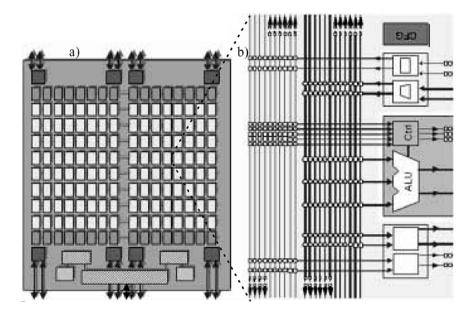

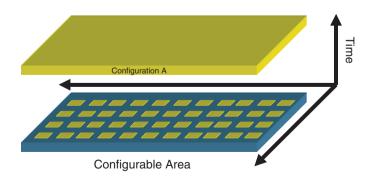

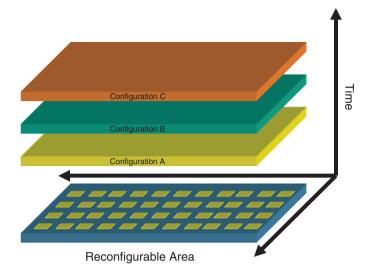

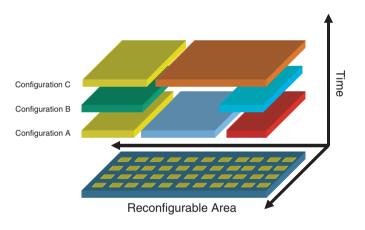

| <ul> <li>20</li> <li>Basics of Reconfigurable Computing</li> <li><i>Reiner Hartenstein and TU Kaiserslautern</i> <ol> <li>Configurable Cells</li> <li>von Neumann vs. Reconfigurable Computing Paradigm</li> <li>Future of FPGA (Technologies)</li> <li>Coarse-Grained vs. Fine-Grained Reconfigurability</li> <li>History of FPGAs</li> <li>References</li> </ol> </li> </ul>                                                                                                                                                              | 451<br>459<br>466<br>476<br>478<br>487<br>489                             |

| 21                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 503                                                                       |

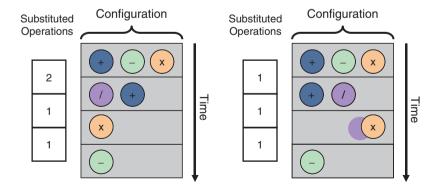

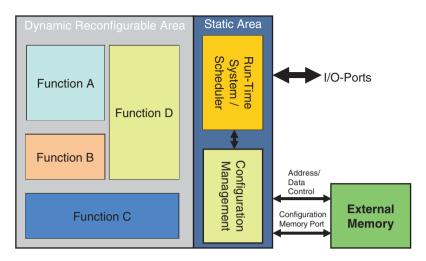

| <ul> <li>Dynamic Reconfiguration</li> <li><i>Jürgen Becker and Michael Hübner</i> <ol> <li>Basis of Reconfiguration and Terminology</li> <li>Exploiting Dynamic and Partial Reconfiguration<br/>for Power-Reduction</li> </ol> </li> <li>References</li> </ul>                                                                                                                                                                                                                                                                              | 503<br>504<br>506<br>511                                                  |

| 22                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                           |

| Applications, Design Tools and Low Power Issues<br>in FPGA Reconfiguration                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 513                                                                       |

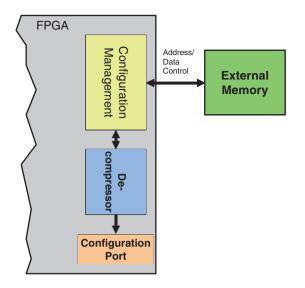

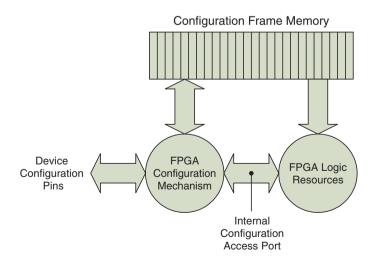

| <ul> <li>Adam Donlin <ol> <li>Introduction</li> <li>Applying Reconfiguration <ol> <li>Applications of FPGA Reconfiguration</li> </ol> </li> <li>Design Flow for Reconfigurable Systems <ol> <li>Dynamic Reconfiguration Design Flow</li> <li>Deploying Dynamic Reconfiguration</li> </ol> </li> <li>Low Power and FPGA Reconfiguration <ol> <li>Low Power and FPGA Reconfiguration</li> <li>The FPGA Low Power Landscape</li> <li>Low Power Use Cases for Dynamic Reconfiguration</li> </ol> </li> <li>Acknowledgments</li> </ol></li></ul> | 513<br>514<br>516<br>522<br>523<br>529<br>532<br>532<br>532<br>535<br>539 |

| Acknowledgments<br>References                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 539<br>540                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                           |

## Foreword

## **Embedded Processors – What is Next?**

Jörg Henkel and Sri Parameswaran

These are exciting times for the system level designer/researcher. The world seems to burgeon with embedded systems. Consumers demand superior electronic products more often than ever before. Moore's law continues to be valid 40 years after it was first stated, allowing the adventurous to design with billions of transistors. Demanding managers require products in shorter time than previously. All of this has led to an unending search for superior methods and tools to design embedded systems.

Interminable appetite by consumers for portable embedded systems has continued to churn out chips with ever growing functionality. Soaring nonrecurring engineering costs of chips has forced designers towards large scale chips which exhibit computation capability along with communication protocols. These designs are expected to be flexible by being software upgradeable, reduce time to market by being rapidly verifiable, and produced in large volumes to reduce the cost per chip. To truly make such systems ubiquitous, it is necessary to reduce the power consumed by such a system. These often conflicting demands have meant that chips have to exhibit smaller footprint and consume less power. For a long time now, the narrowing feature sizes of chips and continuously reducing supply voltages were sufficient to satisfy the size and power demands. Unfortunately, this trend towards smaller feature sizes and lower supply voltages is slowing due to physical limitations. This has led to looking at system level methods to reduce power in embedded systems.

Unlike circuit level methods to reduce power, system level methods often allow a plethora of techniques to be applied at various levels. Often these techniques are orthogonal to one another, and can be applied simultaneously, assuming that the designer has sufficient time. Some of these techniques are at the architecture level-such as application specific processors, some are run-time techniques-which respond to the workload by switching voltage and frequency, some are at design time-such as compiler techniques which allow lower power consumption of the compiled code.

Time is indeed changing the way we design systems. Reducing design time and the size of a design team are increasingly crucial. Numerous tools and methods are available to educated designer. Many of these are point tools, though several tool vendors work tirelessly towards making these point tools interoperable so that seamless design flows can be created, which are useable by designers, increasing productivity several times. While such design flows from the RTL level down are quite mature, the design tools and flows at the system level are still evolving and will evolve for some time to come. Research in this area is very much alive at this time and will be for the foreseeable future.

This book examines system level design techniques, which allow the automation of system level designs, with a particular emphasis towards low power. We expect researchers, graduate students and system level designers to benefit from this book. The authors of the individual chapters are all well known researchers in their respective fields.

### 1. Philosophy of This Book

In order to provide a maximum degree of usability for novices and researchers alike, the book is organized in the following way: each of the individual six sub-topics comprises one section that introduces to the whole area. For example, the section Application Specific Embedded Processors starts with the chapter Designing Application Specific Embedded Processors. That chapter gives an introduction to the field in a textbook-like style along with a mentioning of the specific grand challenges followed by a review of the most relevant related work. Thus, the first chapter of a section introduces a novice to the field. Experts in the respective fields may skip that chapter. The subsequent chapters then pick a research topic and present state-of-the-art research approaches that are representative and most challenging from the current perspective. If too specific, more generally interested readers may skip those chapters. In that sense, the book is useful for both, the expert researcher as well as the novice. Also in that sense, this book provides a new (and hopefully useful) concept.

### 2. Contents

Though there are certainly many more aspects in designing embedded processors with respect to low power, we had to restrict the book and eventually identified six main topics (according to the six sections) namely: I. Application

#### Foreword

Specific Embedded Processors, II. Embedded Memories, III. Dynamic Voltage and Frequency Scaling, IV. Compiler Techniques, V. Multi-Processors, and VI. Reconfigurable Computing. These topics comprise the most relevant techniques to minimize energy/power consumption from a system-level design point of view.

Starting with Section I, Application Specific Embedded Processors, explores optimization energy/power optimization potentials through architectural customizations ranging from application-specific instruction extension through parameterization etc. After the introductory section by Henkel, Parameswaran entitled Designing Application Specific Embedded Processors, the so-called NISC approach by Gorjiara, Reshadi, Gajski is presented in the chapter Low-Power Design with NISC Technology. It describes a novel architecture for embedded processors that does not use instructions in the traditional way any more. The chapter entitled Synthesis of Instruction Sets for High Performance and Energy Efficient ASIP by Lee, Choi, Dutt focuses on reducing the energy-delay product of instruction-extensible through synthesis. The chapter A Framework for Extensible Processor-based MPSoC Design by Sun, Ravi and Raghunathan with an approach to utilize the energy/power efficiency of extensible processors in the context of a multi processor system. This section concludes with Design and Run-Time Code Compression for Embedded Systems. Parameswaran, Henkel, Janapsatya, Bonny and Ignjatovic show the increase in efficiency for an embedded processor when code compression is used.

Section II, Embedded Memories, addresses energy/power related issues around memories, in specific application memories may account for largest fraction energy/power consumption in an embedded application. It starts with the chapter Power Optimization Strategies Targeting the Memory Subsystem by P. Panda with an overview and review of the challenges in embedded memories. The following chapter Layer Assignment Techniques for Low Energy Multi-Layered Memory Organizations by Brockmeyer, Durinck, Corporaal, Catthoor that exploits layered memory assignments for energy/power efficiency. Finally, the chapter Memory Bank Locality and Its Usage in Reducing Energy Consumption within this section exploits the bank locality property to minimize energy.

Section III is dedicated to Dynamic Voltage and Frequency Scaling one of the most efficient techniques for reducing energy/power consumption as to the relationship given by power,  $V_{DD}$  and operating frequency of a switching CMOS transistor. S. Hu et al. give an introduction to the field within the first chapter Power Aware Scheduling followed by Dynamic Voltage and Frequency Scheduling by S. X. Hu et al. presenting new techniques. The chapter Voltage Selection for Time-Constrained Multi-Processor Systems applies the traditional one-processor approach to multi-processors. The role of the compiler i.e. the design-time phase is content of Section IV Compiler Techniques staring with the introductory chapter Compilation Techniques for Power, Energy, and Thermal Management by U. Kremer. The chapter Compiler-Driven DVFS by Hsu, Kremer presents an approach how DVFS can efficiently be incorporated into the the compiler i.e. how this job that is typically decided upon by the run-time system is part of a design time step (i.e. compilation phase). The contribution Link Idle Period Exploitation for Network Power Management by Li, Chen and Kandemir uses the compiler to optimize power consumption of communication links.

Section V is dedicated to Multi-Processors an efficient means to reduce the energy/power consumption as increasing the operating frequency is not an option for increasing the performance any longer because of the power problem. The first chapter A Power and Energy Perspective on Multi-Processors by G. Martin gives an overview of various architectural alternatives and their characteristics with respect to low power. It is followed by the chapter System-level Design of Network on Chip Architectures by Chatha and Srinivasan focusing on a network-on-chip architecture for multi-processors. Paul and Meyer present a modeling approach in the chapter Power-Performance Modeling and Design for Heterogeneous Multiprocessors. Finally, Section VI deals with reconfigurable computing, a computing paradigm that is very promising in solving many energy/power related issues. The first section by R. Hartenstein gives an overview of reconfigurable computing and its suitability for energy/power efficient systems in the chapter Basic of Reconfigurable Computing. It is followed by the chapter Dynamic Reconfiguration a technique to increase energy/power efficiency. The book concludes with the chapter Applications, Design Tools and Low Power Issues in FPGA Reconfiguration. It focuses on reconfigurable fabrics, namely FPGAs and there usage through design tools when low energy/power is an issue.

We hope that this book helps to increase awareness of the main issues in the design of low power embedded processors.

Application Specific Embedded Processors

## Chapter 1

## **Application-Specific Embedded Processors**

Jörg Henkel<sup>1</sup>, Sri Parameswaran<sup>2</sup>, and Newton Cheung<sup>3</sup>

<sup>1</sup>University of Karlsruhe (TH) Germany

<sup>2</sup>University of New South Wales Australia

<sup>3</sup>VaST System Australia

Abstract Today's silicon technology allows building embedded processors as part of SoCs (systems-on-chip) comprising upto a billion of transistors on a single die. Interestingly, real-world SOCs (in large quantities for mainstream applications) utilizing this potential complexity do hardly exist. Another observation is that the semiconductor industry a couple of years ago experienced an inflection point: the number of ASIC (Application Specific Integrated Circuits) design starts was outpaced by the number of design starts for Application Specific Standard Products (ASSPs). Moreover, we might face a new design productivity gap: the "gap of complexity" (details and references will follow later). Together these observations are reflecting a transition in the way embedded processors are designed. This article reports on and analyzes current and possible future trends from a perspective of embedded system design with an emphasis on design environments for so-called extensible processor platforms. It describes the state-of-the-art in the three main steps when designing an extensible processor, namely Code Segment Identification, Extensible Instruction Generation, Architectural Customization Selection.

Keywords: Embedded processors, ESL, design gap

#### **1.** Introduction and Motivation

Embedded systems are ubiquitous and represent the major source of demand for micro-processors with a 10-digit number of units finding their way into embedded system designs every single year. Examples span from security systems (e.g. video surveillance), control systems (e.g. automotive control), individual health systems (e.g. hearing aids) to main stream consumer products in such areas as personal communication (e.g. cell phones), personal computing (e.g. PDA), entertainment (e.g. MP3 players), video/photo (e.g. digital still/video cameras) and many more.

It can be observed that especially the latter group of main stream consumer products is subject to severe competition between major manufacturers and thus leading to two effects from a consumer's point of view:

- The life cycles of embedded products become increasingly smaller: cell phones represent one of many examples for this trend since they experience the introduction of an average of two new major product lines every year compared to only one years ago.

- The functionality of these products and hence the complexity of the underlying embedded systems is rapidly increasing: staying with cell phones as an example, the observation is that they feature far more functionality beyond their core functionality of providing a wireless voice channel and thus establishing a phone connection. In fact, common functions of cell phones include web browsing capabilities, SMS (Short Message Service), PDA functionalities and even gaming, etc. Almost on a monthly basis there are new features manufacturers of cell phones and service providers announce and eventually integrate into new generations.

Similar scenarios could be discussed in conjunction with other consumer, control, etc. devices as well. The observation would often be an increasing portfolio of functionality combined with decreasing product life cycles. In the following these observations are put in relation with trends in embedded system design.

The consumer's demand for increasing functionality translates directly into increased complexity of embedded systems on a chip.

Indeed, this demand matches well with predictions from the International Technology Roadmap for Semiconductors where within this decade a complexity of 1 billion transistors on a single chip is predicted.

However, already today it can be observed that the maximum possible amount of transistors (silicon-technology-wise) per chip is hardly exploited. This fact is even more obvious when the number of transistors per SOC *without* the embedded memory (i.e. easy to design regular structures) is counted.

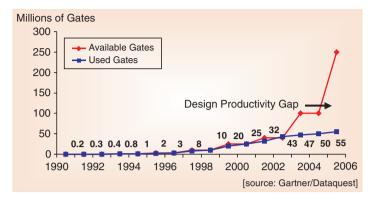

*Fig. 1.1* The "Crisis of Complexity" in case no ESL methodologies will be used (G. Smith, Panel at 40<sup>th</sup> Design Automation Conference, 2003)

In short, real-world SOCs' complexities lag behind the capabilities of current silicon technologies even though there is certainly a demand for higher complexities (i.e. increased functionality) from an application point of view as discussed before.

Figure 1.1 (G. Smith, Panel at  $40^{\text{th}}$  Design Automation Conference, 2003) gives a possible answer: shown is the predicted productivity gap. It is measured as the number of available gates per chip for a given silicon technology for SOCs on the one side (red graph) and the number of actually used gates per chip of a given silicon technology on the other side (blue graph). The gap was predicted for the case that there will be *no* ESL (Electronic System Level Design) methodologies deployed for designing future complex SOCs. In other words: the gap might have been avoided if more ESL methodologies would have been deployed in all areas of system level design like specification/modeling, synthesis, simulation/verification, estimation, etc.

Though the need for ESL methodologies has been predicted and solutions have been researched for many years in the according areas, it is just about to start being accepted by system design engineers. An example is the migration to the so-called C-based design methodologies that represent a raised level (up from RTL) of abstraction in designing digital systems. Beyond a raised abstraction level, ESL methodologies also require an extensive IP component reuse through platforms.

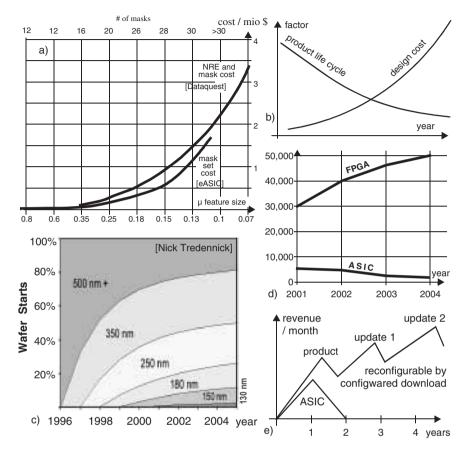

Besides the gap of complexity, there is another indicator for the change (or need of change) of designing complex SOCs: the decrease of ASIC design starts. The number of design starts for ASICs were some years ago, outpaced by the number of design starts for ASSPs (Lewis, 2002). Thereby, the definition (as to Gartner) is as follows: an ASIC is an integrated circuit customized for a specific application that comes in form of a gate array or cell-based IC. An

ASSP (Application Specific Standard Product) on the other side includes all other ICs, i.e. ICs that are used in more than one application like DSPs, etc. In 2002 the number of ASIC design starts amounted world-wide to about 3,500–4,000 with a predicted steady decline over the next couple of years whereas ASSP design starts are predicted to stay steady at around 5,000 per year.

A reason for the declining ASIC design start are the extensive NRE costs when migrating to technology nodes far beyond 100 nm.

In order to overcome the problems of demand for increased functionality in embedded systems at constantly shortening product life cycles, more systemlevel design methodologies combined with the platform-based design paradigm need to be deployed.

#### **1.1** Some Trends in Designing SOCs

Early embedded SOCs were of low complexity as they typically comprised one to two (programmable) processing units (e.g. a micro-controller plus a DSP), some custom hardware, peripherals and memory. However, the number of processing units in today's SOCs is steadily rising. An example is a TCP/IP protocol processing SOC that comprises 10 CPUs on a single chip (NEC, 2003). Each of the CPUs is an extensible processor. The design was preferred over a custom-logic (ASIC) design because it was considered too design-time extensive (and therefore expensive) given the large complexity. On the other side, using general purpose CPUs instead of the actually deployed configurable processors would not have led to the required performance at the same chip complexity (i.e. gate count).

There are other examples for SOCs comprising 10 or more processor including WCDMA chips with close to 15 programmable processing units. Recently (2007) an 80 core chip was announced. So, besides the earlier mentioned increasing functionality of embedded SOCs, there are further trends leading to a rising number of programmable processing units per SOC:

• Complex custom-logic blocks in SOCs are increasingly replaced *in whole* by programmable processing units with high performance. Reasons are the faster SOC development times and thus lower NRE costs at comparable performance values using a new breed of configurable processors (discussed later).

This general trend has similarities to a trend that ended the hey days of super computing when the world's leading supercomputers were made of custom processors with custom technologies. It turned out that they were too expensive to develop given the relatively short life cycles. Today's supercomputer on the other side consist of off-the-shelf microprocessors. Similarly, instead of using expensive complex custom logic blocks, offthe-shelf processors with high performance will increasingly be used in future SOCs.

• Certainly, custom-logic blocks will continue to remain on embedded SOCs for various reasons like very high performance, ultra-low power, etc. However, the complexity of these blocks will shrink since *sub-blocks* of these complex custom blocks will most likely be migrated into low complexity processing units where possible as recent designs show. This is accomplished through processors with a very basic instruction set and low architectural complexity of typically only around 10k–20k gates that run a software program to provide the replaced functionality. Hence, these processors further replace parts of complex custom-logic blocks where high performance/low power, etc. is not necessarily required and thus traded in lieu of a higher flexibility (programmable versa hardwired logic), lower NRE and lower per unit costs.

Both trends together increase the number of programmable processing units on SOCs and decrease the allover gate count for custom-logic per SOC and hence contribute partly to the trend of declining ASIC design starts in favor of ASSPs (see above).

The continuation of this trend is what is predicted to evolve into the "Sea of Processors" (Rowen, 2003) ("The SOC Processor is the new Transistor", D. Patterson, UC Berkeley). The future of embedded systems is likely to be SOCs with hundreds of heterogeneous processors on it by the end of the decade. Designing these *heterogeneous* multiprocessor SOCs will be a challenge and quite different from designs from the parallel computing domain where processing units tend to be homogeneous.

#### **1.2** Extensible Processor Platforms as a Possible Solution

The solution to overcome the gap of complexity is likely to be the migration of custom hardware into programmable processing units, i.e. the increased usage of off-the-shelf components in form of *extensible processors*.

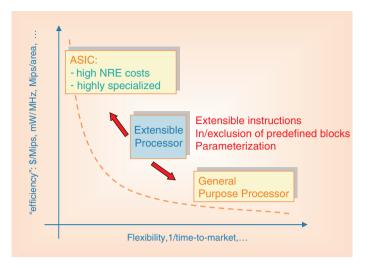

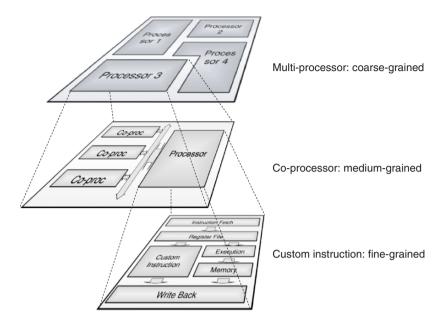

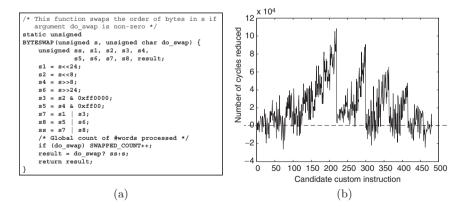

Since the 1990s ASIPs (Application Specific Instruction-Set Processors) have been researched and developed as a compromise between high performance, high cost and low flexibility hard-wired custom logic on the one end and general-purpose processors (GPP) with a high flexibility (i.e. programmability) and more or less moderate performance and power characteristics on the other end (Figure 1.2). The application-specific instruction sets of ASIPs are domain-specific like instruction sets for multi media, encryption/de-cryption, etc. and thus result in increased performance-per-(chip-)area ratios compared to GPPs. Extensible processor platforms represent the state-of-the-art in ASIP technology. The customization of an extensible processor comprises typically

Fig. 1.2 Custom hard-wired logic, extensible processor and general purpose processor

the following three levels *instruction extension*, *inclusion/exclusion of pre*defined blocks, parameterization:

• Instruction Extension

The designer has the choice to freely define customized instructions by describing their functionality in a high-level language. This description is used by the platform's design flow as an input and subsequent synthesis steps will generate according custom instructions that are co-existing with the base instruction set of the extensible processor. Practically, restrictions may apply: for example, the complexity of an instruction (in terms of number of cycles for execution) may be limited in order to accommodate the according data path into the pipeline architecture of the base core. Also, the designer of the custom instructions may be responsible for a proper scheduling when instructions require multi-cycling. Other restrictions may constraint the total number of extensible instructions that can be defined and integrated per processor, etc.

• Inclusion/Exclusion of Predefined Blocks

Predefined blocks as part of the extensible processor platform may be chosen to be included or excluded by the designer. Examples are special function registers, built-in self-test, MAC operation blocks, caches etc.

• Parameterization

Finally, the designer may have the choice to parameterize the extensible processor. Examples are: setting the size of instruction/data caches,

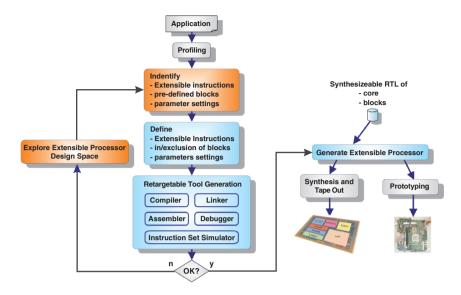

Fig. 1.3 A typical design flow for designing extensible processors

choosing the endianness (little or big endian), choosing the number of registers and many more.

Commercial platforms for extensible processors have been on the market for a while. Major venders of extensible processor platforms include Tensilica, Improv Systems, ARC as well as Coware's LisaTek platform, Target Compiler and others. The latter two pursue a slightly different approach as their focus is directed towards retargetable tool generation (see later) and as they provide means to define/simulate/synthesize a whole new instruction set architecture rather than extending an existing one.

In the following a typical design flow of an extensible processor platform is shortly described<sup>1</sup> with respect to open issues for research.

Figure 1.3 shows the basic steps with the goal to customize the extensible processor to a specific application which might be available in C/C++ description. A profiling by means of, for example, an ISS (Instruction Set Simulator) of the target processor unveils the bottlenecks by cycle-accurate simulation, i.e. it shows which parts of the application represent the most time consuming ones (or, if the constraint is energy consumption, which are the most energy consuming ones). The results of the profiling are the basis for the designer to *identify* (see Figure 1.3) possible instruction extensions, inclusion of predefined blocks and parameterization.

<sup>&</sup>lt;sup>1</sup>Please note that is a generic flow only that may or may not cover a specific vendor's platform capabilities. For vendor-specific features please refer to the vendor's web pages.

Finding the right combination of these three major ways of customization is an art and requires an experienced designer. Once, the identification has been completed, the designer starts *defining* (see Figure 1.3). The most important part of this step is the defining of a set of extensible instructions. This is typically done by a custom language that allows to specify an extensible instruction's functionality, scheduling within the pipeline, instruction word format, etc.

After this step is completed, the designer wants to verify that the various customization levels of the extensible processor meet the given constraints (performance, power, etc.) associated with the application. This can be accomplished by retargetable tool generation: simply said, retargetable tool generation is a technique that allows to *retarget* compilation/simulations tools to any architecture. Say, for example, the ISA of an extensible processor is enhanced by a new set of customized instructions. Retargetable techniques then allow to automatically generate a compiler that is aware of the new instruction, i.e. it can generate code and optimize using the recently defined extensible instructions. Accordingly, an ISS is able to cycle-accurate simulate an executable that contains newly defined instructions, etc.

ISS, compiler assembler are then used in the next step to verify in how far the application-imposed constraints can be met using the three discussed customization levels. This is an important step and it can be iterated very fast and thus gives the designer an early feedback through what is called *design space exploration* before synthesis and tape out takes place. In case the designer is satisfied with the simulation results, the specification of instruction definitions and other customization levels are used to *generate* (Figure 1.3) synthesizeable RTL of the extensible processor. This is done by means of a library that contains the synthesizeable RTL of the base processor core. Then, the regular synthesis follow down to the tape out or an evaluation using a rapid prototyping environment follows.

In summary, designing an embedded system using configurable processors as building blocks in a multiprocessor SOC environment represents an efficient way to overcome the complexity gap and will further contribute to the domination of ASSP design starts.

### **1.3** Open Issues and Key Techniques

The above-mentioned scenario of multiprocessor SOCs replacing traditional domains of custom hardware through extensible processor platforms has still open issues that need more research. Some of them are listed shortly:

• What is the optimum set of extensible instructions for a given application? Currently, the designer of customizable processors does have the means to evaluate instruction extensions on a high level (retargetable ISSS, etc.) without going through the large turn-around time of implementation first followed by evaluation. However, it is currently entirely up to the designer's experience to identify the kind and granularity of instructions that represent the best return on investment (i.e. chip area) and thus to efficiently explore the extensible processor's design space. Those and similar issues are currently being researched and presented at major design automation conferences like *DAC*, *ICCAD*, *DATE* and others.

- How will all those processors on a SOC communicate with each other? Clearly, traditional on-chip bus systems will not be able to handle the increased traffic when several dozens of heterogeneous processors are integrated on a chip and have to heavily communicate with each other. NOCs not only provide higher bandwidths but they are also scaleable, etc. It is currently an open issue of how an efficient on-chip communication network will look like. Here too, high-level design methodologies are needed to design a custom on-chip network that satisfies the constraints of an embedded application best. The field of architectures and design methodologies for NOCs is currently being researched.

- Retargetable Tool Generation Through several years of research, retargetable tool generation has made significant progresses. However, there are many open issues with respect to extensible processor platforms like, for example, the capability of retargetable compilers to efficiently include extensible (i.e. designer-defined) instructions during the optimization phases etc.

## **1.4 SOC Design Distinction**

Custom-logic hardware blocks in an embedded SOC system are often credited for the SOC's key characteristics that distinguish a certain SOC design of vendor A from a competitive one of vendor B. Those key characteristics include performance, power consumption, etc. With a continued migration of custom logic into programmable processing units, as discussed earlier, design distinction is shifting, too.

Finding the right set of adapted and optimized extensible instructions is an art given the large design space (extensible instruction; inclusion of predefined blocks; parameterization) of extensible processors.

In addition, the processors need to be programmed, hence shifting more and more design expertise into software. An indicator is the increasing size of embedded software: recent designs feature more than a million lines of embedded code tendency rising. Already today, there are many design examples where embedded software takes more resources (engineers) than the hardware design of a SOC. **Conclusion.** The complexity gap will most likely not occur meaning that possible SOC complexities (silicon-technology-wise) of a billion transistors at the end of the decade will be fully exploited by mainstream embedded systems SOCs. Clear indication is an increasing usage of system-level design methodologies and a migration of custom logic into programmable processing units wherever design constraints (performance, power) allow for. A promising approach are extensible processors. In the following, the major challenges when designing an embedded extensible processor are explained.

## 2. Challenges in Embedded Extensible Processor Design

Typically, a great amount of expertise is necessay to design extensible processors. The challenging tasks are *code segment identification*, *extensible instruction generation*, *architectural customisation* and *processor evaluation*, which are usually conducted manually. Therefore, recent research has largely focused on these design tasks, and has sought to optimize and automate various steps. This section describes the problems associated with these design tasks and some of the solutions proposed in the literature.

## 2.1 Code Segment Identification

In order, for example, to increase the performance of an application, code segments can be sped up by generating extensible instructions, including/excluding predefined blocks and setting parameteriations. However, the code segments first need to be identified from the application. While identifying code segments is somewhat supported by profiling tools, it is still a daunting task for large applications, and further complicated when additional constraints (e.g. area and power) must be optimized as well as. Furthermore, the number of code segments for a given application grows large with the program size. It is very common for a function with fewer than one hundred operations to contain several hundred possible code segments.

Recent research can be classified into three categories:

- 1. Retargetable code generation using matching and covering algorithms

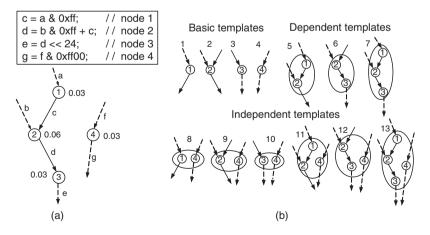

- 2. Finding patterns in the graph representation (control dataflow graph) of the profiled application

- 3. High-level extraction from the application

It follows an overview.

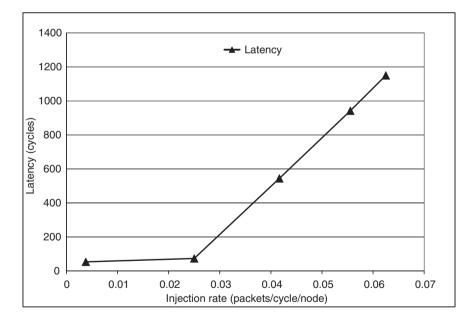

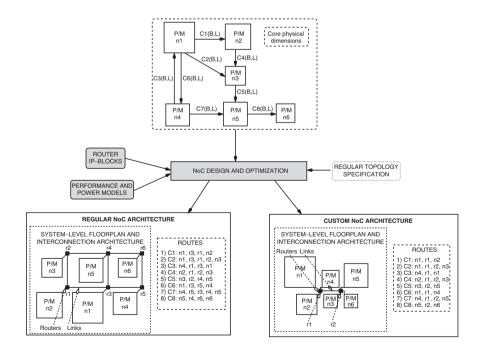

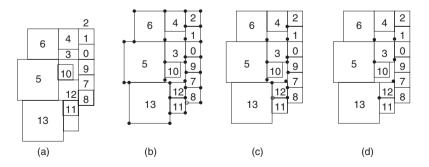

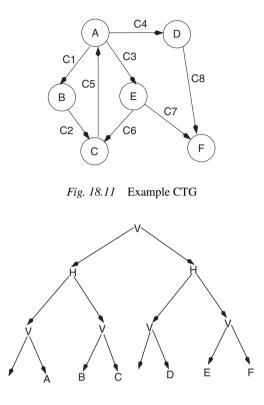

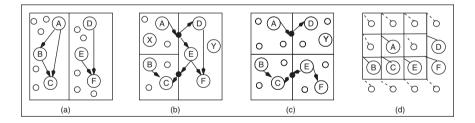

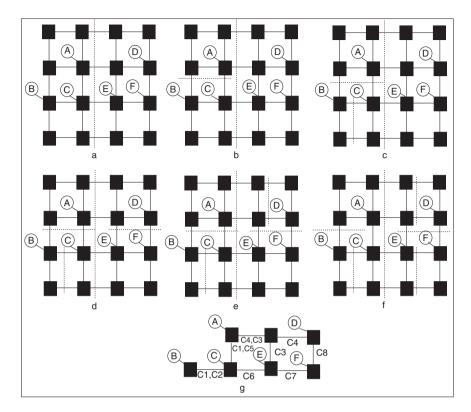

**Code Generation Using Matching Algorithms.** Code generation using a matching algorithm is a well-known problem, particularly in the fields of technology mapping in logic synthesis (Keutzer, 1987; Cong and Ding, 1992;